日誌

為何功率MOSFET P-ch 比 N-ch 貴又規格差?

載子遷移率(carrier mobility)

載子遷移率用於描述金屬或半導體內部電子與電洞,在電場作用下移動快慢程度的物理量。

在半導體低摻雜矽材料中,

N材料是電子在移動用電子遷移率(electron mobility)1350單位,

P材料是電洞在移動用電洞遷移率(hole mobility)為480 單位。

遷移率單位(cm平方)/(伏*秒) ,載子遷移率是概括兩者合稱。

就像電導率解釋了 銅59.6 × 10^6比鋁37.8 × 10^6 導電能力佳,

N材料電子遷移率 好過 P材料電洞遷移率。

比對先前那段話:用電子推擠其他電子移動 易於 電洞吸引電子造成電洞傳遞

這就是同製作技術與額定電流規格下,P材料要用更多體積才能追上N材料。

所以常常功率元件選用更具成本效益的N材料。

若有機會看到積體電路layout 注意其推挽輸出的 P材料總會比N材料用了較多空間,

無論是BJT電晶體亦或FET場效 都相同。

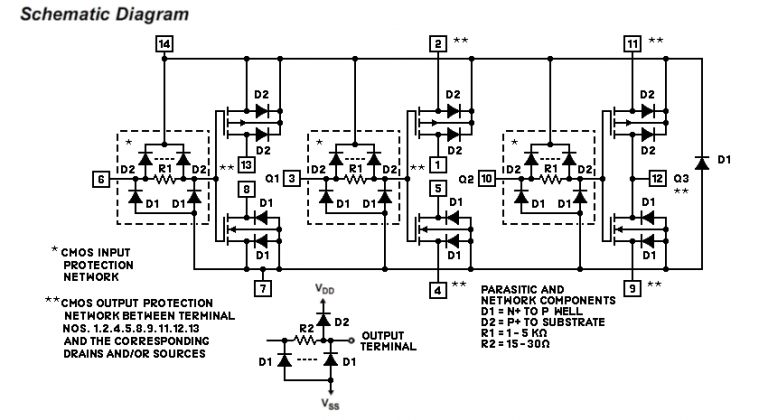

下圖是CMOS 邏輯積體電路 CD4007 的接腳sch線路圖 來源取自TI DATASHEET

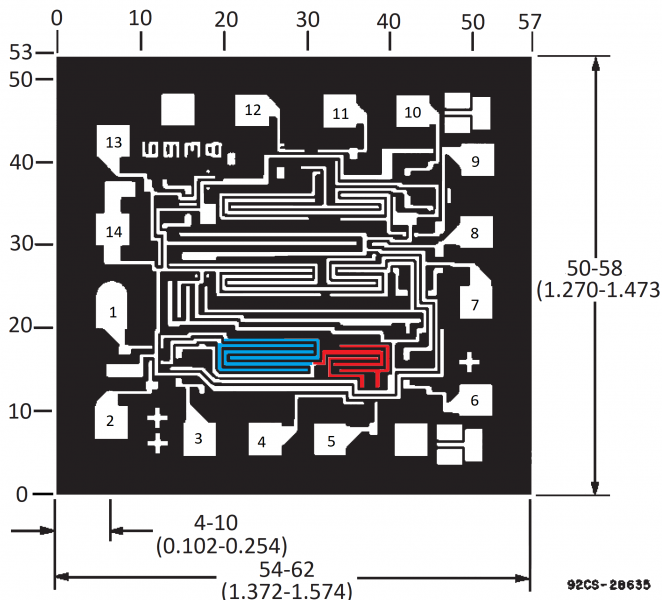

下圖是CMOS 邏輯積體電路 CD4007 的Layout佈局圖 來源取自TI DATASHEET

青藍色區塊 分接[1_S][2_D][3_G]腳 這是P_MOS

而紅色區塊 分接[4_S][5_D][3_G]腳 這是N_MOS

明顯PMOS佔用空間大於N_MOS