|

|

本帖最後由 xiaolaba 於 2019-10-23 12:03 AM 編輯

以前學習過, JFET 的 DS 連在一起就是一個超低漏電流的DIODE, 據說一般DIODE是nA級, 這種JFET短接DS是 pA 級以下, 既能夠保護OPA輸入端, 又不會影響測試訊號. http://www.ti.com/lit/an/sboa058/sboa058.pdf

也看過這裏前輩演示 BIPOLAR TRANSISTOR 接通 BC 腳成為高壓的 ZENER DIODE 的用法, 所以DMM裡面都有兩個, https://bbs.pigoo.com/thread-71102-1-1.html

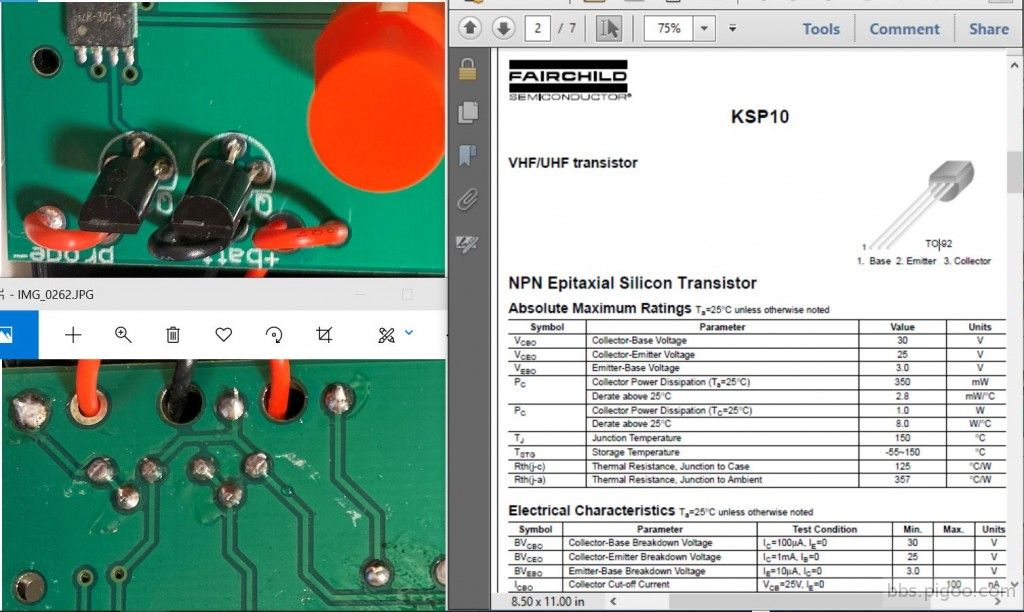

後來又拆了一個表, 粗略測試 1K 到 1000G 電阻的, 裡面是專門的IC, HZR-301, 找不到資料的, 很可能是 LOG AMPILIFER. 不過輸入端有另外一種設計, Q1 和Q2, 印字都是 KSP10, 應該兩個 NPN, 它的設計是 BE 連在一起接到輸入端, C腳接地, 看不懂原理.

KSP10_BE_CONNECTED_WHY

看了 ANALOG 的解說, 沒有接近的,

https://wiki.analog.com/university/courses/electronics/electronics-lab-3

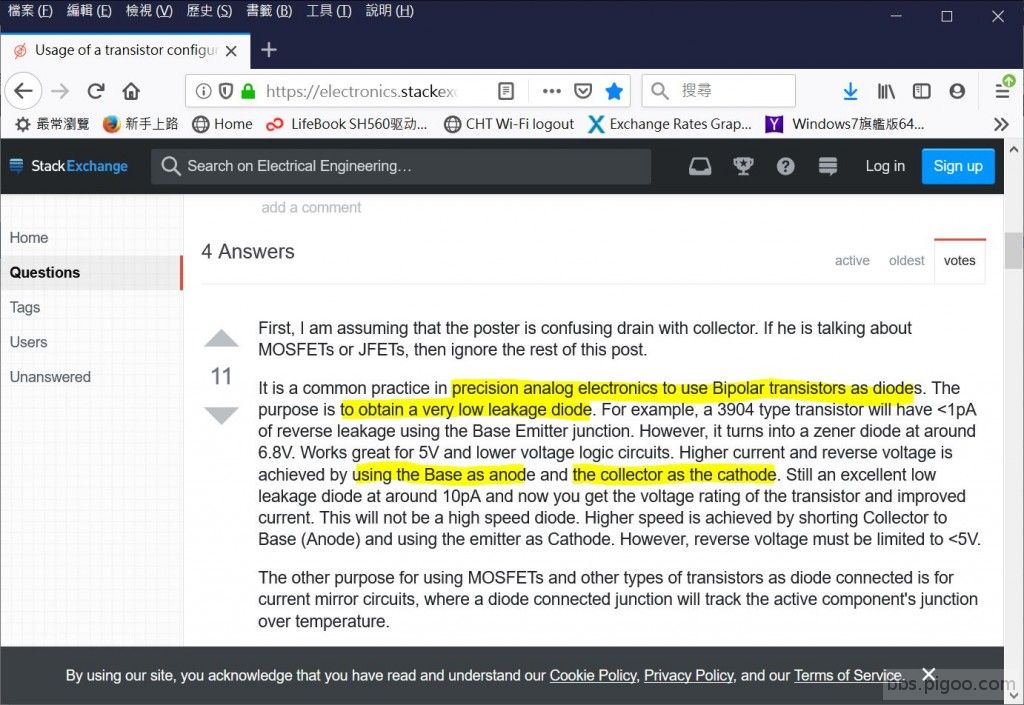

找到的網路資訊, 認為是最有可能接近的解說,

https://electronics.stackexchange.com/questions/50633/usage-of-a-transistor-configured-as-diode

DIODE TRANSISTOR xiaolaba

偶是既沒有精密儀器, 也沒有工具實驗, 純粹想學習它的原理, 大俠們給指點指點它的設計目的為何.

|

|