|

|

樓主 |

發表於 2008-12-28 14:00:59

|

顯示全部樓層

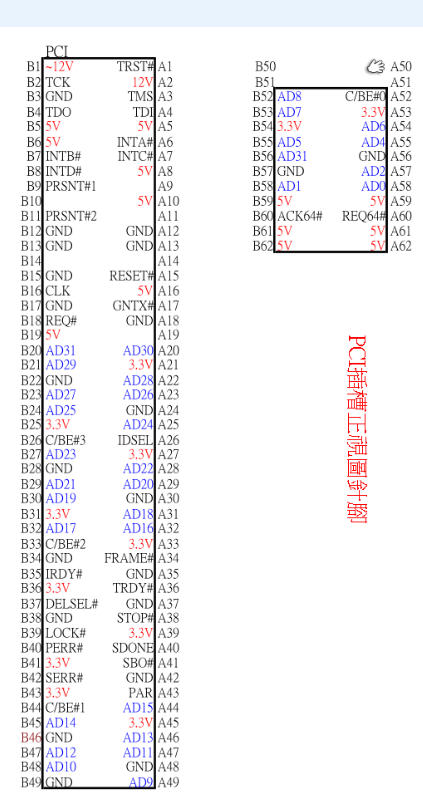

PCI接口信號說明

1. AD[31:0] I/O Address Data Bus(地址數據總線) 是用來傳送起始地址.在內存或組態的交易期間,此地址的分辨率是一個雙字組(Double Word)(即地址可被四整除),在讀取或寫入的交易期間,它是一個字節特定地址.

2. PAR I/O Parity Signal(同位信號)在地址階段完成後一個頻率,或是所有寫入交易的數據階段期間,在IDRY#被驅動到僭態後一個頻率,由Initiator驅動.所有讀取交易的數據階段期間,在TRDY#被驅動到僭態後一個頻率,它也會被目前所尋址的Target驅動.在地址階段完成後的一個頻率,Initiator將PAR驅動到高或低態,以保證地址總線AD[0:31]與四條指令/位組致能線 C/BE#[0:3]是偶同位(Even Parity).

3. C/BE[3:0]# I/O Command/Byte Enable(指令或字節致能)由Initiator驅動,在AD Bus上傳輸地址時,用來表示當前要動作的指令.在AD Bus上傳輸數據時,用來表示在目前被尋址之Dword 內將要被傳輸的字節,以及用來傳輸數據的數據路徑.

4. RST# O PCI Reset(複位信號) 當重置信號被驅動成低態時,它會強迫所有PCI組態緩存器 Master及Target狀態機器與輸出驅動器回到初始化狀態.RST#可在不同步於PCI CLK邊緣的狀況下,被驅動或反驅動.RST#的設定也將其它的裝置特定功能初始化,但是這主題超出PCI規格的笵圍.所有PCI輸出信號必須被驅動成最初的狀態.通常,這表示它們必須是三態的.

5. FRAME# I/O Cycle Frame(周期框架) 是由目前的Initiator驅動,它表示交易的開始(當它開始被驅動到低態時)與期間(在它被驅動支低態期間).為了碓定是否已經取得總線擁有權,Master必須在同一個PCI CLK信號的上邊緣,取樣到FRAME#與IRDY#都被反驅動到高態,且GNT#被驅動到低態.交易可以是由在目前的Initiator與目前所尋址的Target間一到多次數據傳輸組成.當Initiator准備完成最後一次數據階段時,FRAME#就會被反驅動到高態.

6. IRDY# I/O Initiator Ready(備妥) Initiator 備妥被目前的Bus Master(交易的Initiator)驅動.在寫入期間,IRDY#被驅動表示Initiator准備接收從目前所尋址的Target傳來的資料.為了確定Master已經取得總線擁有權,它必須在同一個PCI CLK信號的上升邊緣,取樣到FRAME#與IRDY#都被反驅動到高態,且GNT#被驅動到低態.

7. TRDY# I/O Target Ready(目標備妥) Target備妥被目前所尋址的Target驅動.當Target准備完成目前的數據階段(數據傳輸)時,它就會被驅動到低態.如果在同一個PCI CLK信號的上升邊緣,Target 驅動TRDY#到低態且Initiator驅動IDRY#到低態的話,則此數據階段便告完成.在讀取期間,TRDY#被驅動表示Target正在驅動有效的數據到數據總線上.在寫入期間,TRDY#被驅動表示Target准備接收來自Master的資料.等待狀態會被插入到目前的資料階段裏,直到取樣到TRDY#與IRDY#都被驅動到低態為止.

8. STOP# I/O Stop(停止) Target驅動STOP#到低態,表示希望Initiator停止目前正在進行的交易.

9. DEVSEL# I/O Device Select(設備選擇信號) 該信號有效時,表示驅動它的設備已成為當前防問的目標設備.換言之,該信號的有效說明總在線某處的某一設備已被選中.如果一個主設備啟動一個交易並且在6個CLK周期內設有檢測到DEVSEL#有效,它必須假定目標設備沒能 反應或者地址不存在,從而實施主設備缺省.

10. IDSEL I Initialization Device Select(初始化設備選擇) IDSEL是PCI裝置的一個輸入端,並且在存取某個裝置的組態緩存器期間,它用來選擇芯片.

11. LOCK# I/O Lock(鎖定) 這是在一個單元(Atomic)交易序列期間(列如:在讀取/修改/寫入操作期間),Initiator用來鎖定(Lock)目前所尋址的Target的.

12. REQ# I Request(請求) 表示管理者要求使用總線,此為一對一之信號,每一管理者都有與其相對應之REQ#信號.

13. GNT# O Grant(保證) 表示管理者對總線使用之要求已被同意,此為一對一之信號,每一管理者都有與其相對應之GNT#信號.

|

|